〈工業技術與資訊〉高深寬比玻璃基板電鍍填孔及檢測技術

撰文/唐祖湘

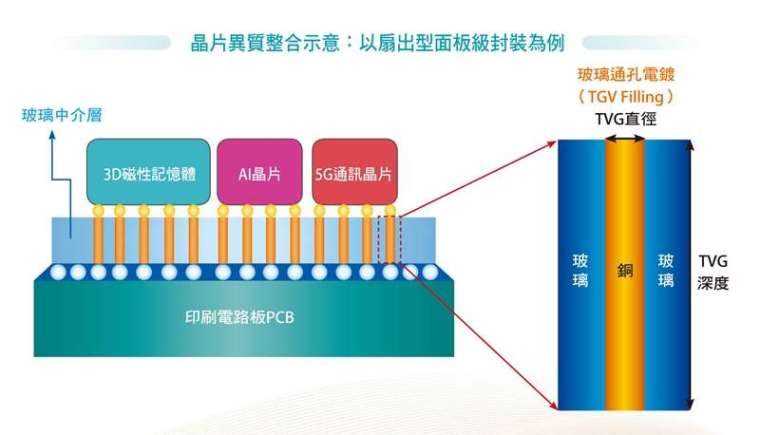

玻璃中介層(Glass Interposer)技術提供 2D 到 3D 先進封裝,更穩定的良率與更具競爭力的成本。隨著半導體製程持續演進,串接各層間的導線深寬比不斷增加,工研院的「高深寬比玻璃基板電鍍填孔及檢測技術」,可有效增加電極密度、改善晶片堆疊,助臺灣半導體產業持續引領風騷,因而獲工研院傑出研究獎金牌。

5G 時代來臨,人工智慧、物聯網、車聯網等應用相繼崛起,為提升晶片效能,半導體持續發展晶片微縮製程,從 7、5 奈米(nm)走向 3、2 奈米,逼近摩爾定律的極限,亟需另闢蹊徑來推動技術演進。其中,透過 2.5D 或 3D 設計,將不同電子元件堆疊,整合在一顆晶片的「異質整合」技術應運而生,成為半導體產業持續前進的突破點。

技術領先 達全球最高深寬比

傳統 2D 封裝是將晶片並排安裝在單一平面上,隨著晶片走向輕薄短小,還要具備高運算、低功耗等高階應用能力,2D 封裝已不足支撐產業需求;3D 封裝突破了水平框架限制,透過異質整合將不同功能的晶片垂直堆疊整合,使得晶片模組運算能力更強。

中介層技術是異質整合的關鍵之一,玻璃中介層擁有低翹曲、訊號傳遞更快、用電效率更佳等優勢,加上符合輕薄需求,近年有後來居上的趨勢。中介層需要內接金屬導線作為上下訊號傳遞的通道,因此會針對玻璃進行穿孔加工,隨著半導體製程的不斷演進,導線孔洞的「深寬比」(Aspect Ratio;AR)持續增加。

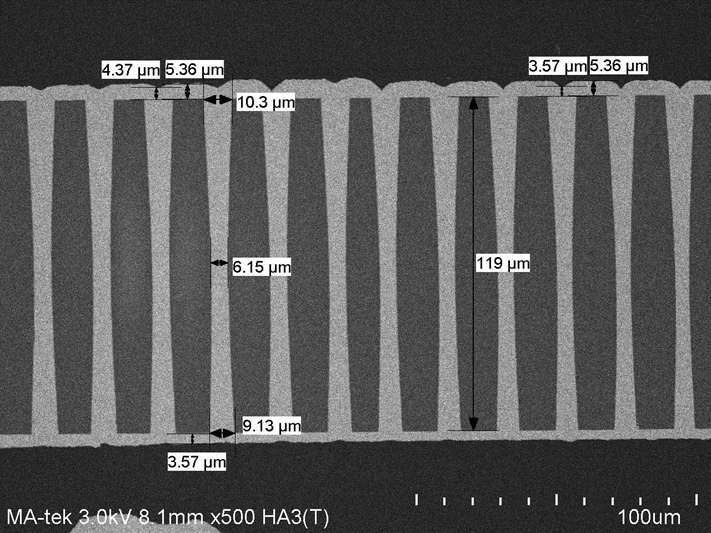

所謂「深寬比」又稱縱深比,指的是導線孔洞深度與直徑的比例。工研院機械與機電系統研究所先進機械技術組副組長黃萌祺說明,3D 晶片堆疊層數越多,孔洞就要打得越深,晶片尺寸變小,線寬線距越來越短,孔洞直徑也就跟著縮減,因此製作小孔徑、高深寬比的方向是必然趨勢。然而深寬比愈高也代表製程愈難,成為產業亟待克服的技術挑戰。

「就像是蓋大樓,一層又一層構築起外觀與骨架,玻璃基板就如樓層間的地板,必須將樓板鑽孔打通,串接上下層的電路、水管等管線,讓水電正常供應,各樓層機能無虞,」黃萌祺提出生動比喻。

工研院耗費 5 年,領先全球研發「高深寬比玻璃基板電鍍填孔及檢測技術」,透過玻璃基板通孔(TGV),連通上下層金屬導線,傳輸電力與訊號,使晶片效能最佳化。「工研院的技術就是要讓大樓蓋得再高,也能保證電訊與電力的傳輸品質!」黃萌祺說。

濕式金屬鍍層沉積技術 成就最高深寬比

國際上對高深寬比的研發不在少數,但 AR 最多只到 10,遠不及工研院的解決方案。而工研院領跑全球的關鍵,有賴三大亮點技術:首先是開發全新填孔電鍍製程,以玻璃通孔基板為中介層,再將銅電鍍上基板填充孔洞,讓電路上下連通。為增加金屬與玻璃的接合度,填孔前玻璃表面需要製作一層 100 至 200 奈米的複合式氧化物導電薄膜,以此作接合的橋樑。

業界是以乾式結合濕式製程來製作導電薄膜:利用真空電漿鍍膜設備(PVD)把金屬打成離子狀態飛入孔洞,但晶片堆疊越多層、孔洞位置就越高,要精準入洞的難度也增加,以致良率下降;工研院開發出低成本、適合高深寬比的「複合式氧化物導電薄膜」,採全濕式製程,透過浸泡無機氧化物與無電鍍銅藥液流經深孔,使其表面產生氧化物薄膜,再經低溫共燒技術,讓金屬氧化物薄膜與玻璃基材產生介金屬化合物,即可克服玻璃與金屬附著力不佳的瓶頸。

「若採傳統製程,深寬比 15 已是極限,」黃萌祺指出,全濕式製程的 AR 可達 15 至 30,晶種層沉積率高於 7 成,覆蓋率佳;且 PVD 機台身價不斐,「從乾濕搭配改成全濕式設備,可節省成本約 5 成,為業者減輕不少壓力。」

單劑雙功能電鍍添加劑 完美無縫填洞

其次是開發具雙功能的單劑型電鍍添加劑填孔配方。一般情況下,以電鍍填充銅金屬時,孔洞表面往往最快形成金屬沉積,中間則最慢,因此容易產生空隙,實際使用時遇到較大電流,晶片會很快損壞,所以需要使用特殊的添加劑,讓孔洞口金屬沉積速度變慢,待孔洞中間填滿後再填洞口,就可減少孔隙產生。

黃萌祺解釋,要解決這個問題,業界普遍同時使用 3 種添加劑,但電鍍時 3 劑各自消耗,需要適時補充,但添加劑會彼此干擾,要補充什麼?補充多少?難以精準掌握。團隊決定甩開這個惱人問題,直接開發新型添加劑,「從一篇篇文獻研究開始,判斷哪些化學藥劑可能符合所需功能,再逐一進行篩選,」黃萌祺說。

經過一段摸索期,團隊找到幾支特定藥劑,展開配方實驗。團隊主要開發成員工研院機械所研究員張佑祥,半年來幾乎天天泡在實驗室,將實驗每個步驟一一記錄,精挑細選出一款不曾使用於電鍍的藥劑,意外的同時具備抑制與平整功能,不用再與其他劑搭配,效果就很出色。「由於是單劑型作填孔電鍍,不但能解決覆蓋率的問題,降低因不同電鍍添加劑所造成的量測干擾,更有效提升製程穩定性與良率,與目前業界配方相比,還能省下 50% 的成本,」黃萌祺興奮表示。

3D 微孔偵測 缺陷無所遁形

第三個亮點則是開發先進的 3D 圓球形演算法(Sphere-Fitting),來檢測高深寬比的銅填孔狀態。黃萌祺透露,這項技術可說是研發過程中最具挑戰、也是最難掌控的部分。結構或藥劑配方,團隊還能自行調整,唯有填孔成效,從外圍到中間有沒有填好填滿?哪裡有孔隙?光憑肉眼與普通顯微鏡都無法觀察,「若忽略這道程序,不知道填充結果,就像矇著眼睛研發,根本無從精進。」

一開始團隊委託外部檢驗單位,光是檢測一片基板就得耗上半天,3D X 光片也需人力逐一檢查,若同時開發多種配方,來回至少要 1~2 個星期,曠日費時。所幸,團隊獲得院內材料領域專家跨刀相助,開發出改良版的 3D 圓球形演算法,經高解析、高對比的奈米斷層掃瞄,電腦軟體針對內部結構之微孔分布與直徑加以演算,精確快速找出缺陷。黃萌祺認為,「這個演算法的最大突破,是可以同時偵測上百根 TGV 銅填孔,最快 1 到 2 天就能知道結果,大幅縮短檢測與校正時間。」

工研院材料與化工研究所博士林子閎表示,類似的孔隙偵測技術多用於生醫材料或原油探勘,例如牙科檢測牙本質小管細微結構、石油業者鑽油探勘油礦等。而將自動孔隙偵測演算法結合奈米斷層掃描 3D 檢測技術,用在電子業則是頭一遭,對材料領域也是新的嘗試。「這個檢測的挑戰在於,銅金屬照 X 光容易造成散射,要讓軟體剔除雜訊與散射,才能進一步建立 3D 立體軸,清晰呈現後,由程式自動且快速鑑別出金屬柱內的孔隙、缺陷位置與軸向定位。定義出精準座標後,電子顯微鏡才能進行精準比對確認,做更高解析度的分析,朝正確的方向調整。」林子閎說。

透過精確的檢測驗證,團隊明顯感受到成果漸入佳境,「早期技術沒那麼完善,內部會有滿大孔隙,像是球棒中間裂開一條縫,隨著技術越改越精良,後期只會出現如花生米一般、2 至 4 微米(㎛)的洞;到了現在,連一點點孔隙都找不到了!」黃萌祺不禁露出滿意的笑容。

為半導體業超前部署 創千億產值

本技術問世,可應用在半導體先進封裝產業中的扇出型面板級封裝(FOPLP)、高密度電路板(HDI PCB)以及 IC 載板,滿足電子產業先進製程的需求。黃萌祺指出,該技術雖然只占封裝製程一部分,但濕式設備與單劑添加劑等重要開發,不僅縮短製程時間,也為業者省下至少 3 成的設備與藥劑成本,估計可創造上千億元的產值。

這項開發計畫的另一層重要意義是促成跨產業的合作,例如提供玻璃基板與鑽孔的國際知名玻璃大廠,原本將主力放在供應顯示器,藉由這次的計畫也跨足半導體領域,獲得新的產品開發方向;而與工研院搭配,設計藥劑設備的 2 家本土設備廠,也是首次跨入半導體先進封裝設備領域,建立次世代的國產設備能量。

黃萌祺透露,目前業界對高深寬比的量產要求 AR 約 7~8,預計 2、3 年後才會提高到 10 至 15,工研院可說是為半導體產業超前布署,目前已在各主要封測廠進行測試,且研發技術仍不斷精進中,盼能早日量產,讓創新落地,讓臺灣持續保有半導體產業的優勢與製程領先地位。

轉載自《工業技術與資訊》月刊第 353 期 2021 年 7 月號,未經授權不得轉載。