台積電 (2330-TW)(TSM-US) 旗下 ASIC 業者創意 (3443-TW) 今 (24) 日宣布,3 奈米 HBM3E 控制器和實體層 IP 已獲領先業界的雲端服務供應商 (CSP) 及多家高效運算 (HPC) 解決方案供應商採用,該顆 ASIC 預計今年將完成設計定案(Tape out),並將採用最新的 9.2Gbps HBM3E 記憶體技術。

此外,創意也積極與 HBM 供應商,如美光 (MU-US) 合作,為下一代 AI ASIC 開發 HBM4 IP。

業界指出,進入 HBM3E 之後,記憶體業者與邏輯晶圓廠間的合作越趨緊密,且未來因應基礎裸晶 (Base die) 改採先進製程製造,也為創意等 ASIC 業者帶來新商機,創意過去長期與 SK 海力士合作,此次又再宣布攜手美光切入 CSP,象徵在 HBM 三大廠中一舉掌握兩家,為後續營運注入強心針。

創意指出,公司通過台積電先進製程技術的驗證,包括 N7/N6、N5/N4P、N3E/N3P 製程,並在台積電 CoWoS-S 及 CoWoS-R 製程均通過矽驗證,分別在製程上設計 eDTC 與 IPD,以實現最佳電源完整性。

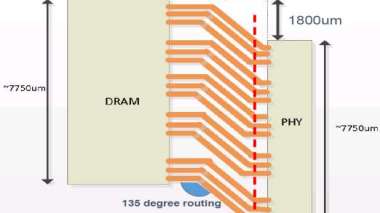

創意在高階中介層 (Interposer) 佈線領域,透過專利中介層佈局,支援具 Y 軸偏移的角度佈線,並保持最佳的信號完整性及電源完整性。創意也可為 HBM CoWoS ASIC 平台設計提供完整的 2.5D 與 3D 服務的選項。

創意也與 proteanTecs 合作,將小晶片互連監視器整合到 HBM PHY 中,可增強小晶片的可觀察性和可靠性。

創意與美光間的合作證明,創意的 HBM3E IP 與美光 HBM3E 可以在 CoWoS-S 和 CoWoS-R 技術上實現 9.2Gbps,創意測試晶片的矽結果顯示,除了電源完整性 (PI) 與信號完整性 (SI) 結果通過考驗,在不同溫度和電壓角落上也取得優異的眼圖邊限。此外,創意 IP 與美光的 HBM3E 時序參數整合時可展現更有效的匯流排利用率,進一步增強整體系統效能。

創意行銷長 Aditya Raina 說,很高興看到公司 HBM3E 控制器和 PHY IP 整合到 CSP 和 HPC ASIC 中,公司 HBM3E 解決方案不但經過矽驗證,也通過多個先進技術與主流廠商的驗證,而持續獲得多家大廠採用,也彰顯該解決方案的穩健度與優勢。期待繼續為各種應用提供支持,包括 AI、HPC、網路和汽車。

美光 AI Solutions Group 的 senior director Girish Cherussery 表示,記憶體是 AI 伺服器不可或缺的一部分,也是資料中心系統效能和進步的基礎。美光同級最佳的記憶體速度及能源效率表現,非常有益於因應 ChatGPT 等大型語言模型這類生成式 AI 工作負載日益增加的需求,進而支援 AI 維持成長步調。